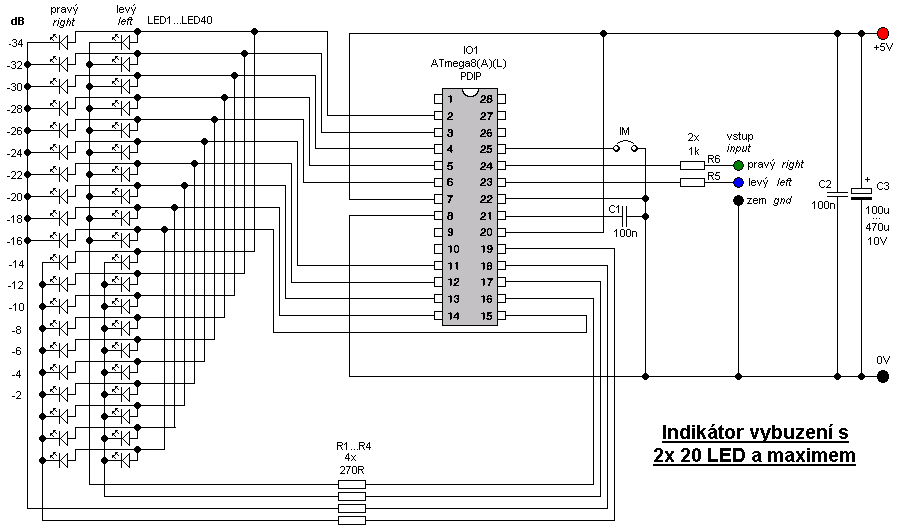

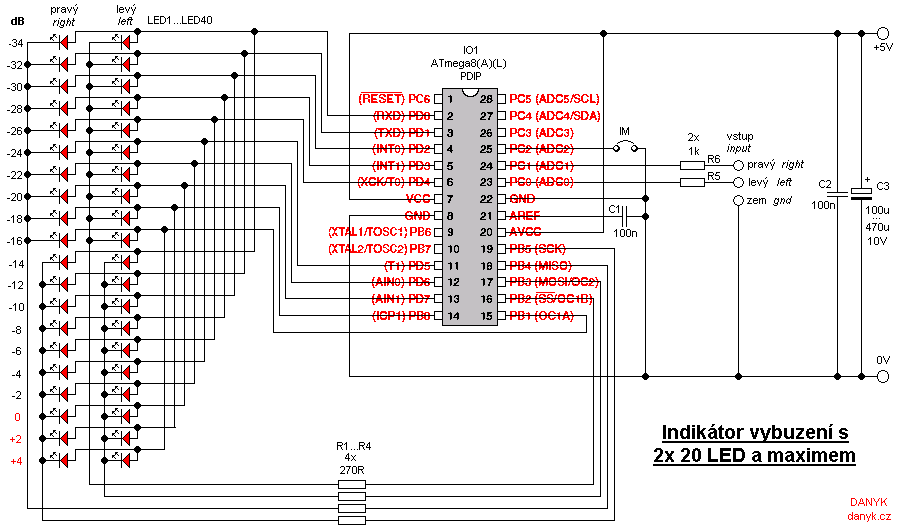

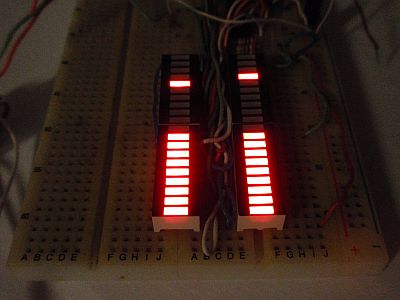

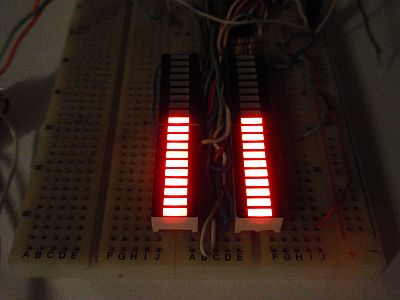

El circuito VuMetro con retención de pico de barras LED puede operar en retención de pico y trabajar normalmente, tiene un indicador de pico LED de 2 × 20. Los leds están controlados por el microcontrolador Atmega8. El rango de visualización es de -34 a +4 dB.

Los LED se controlan multiplexando 4 LED en 10 pasos, la frecuencia de multiplexación es de aproximadamente 100 Hz. R1… R4, su resistencia (270 ohmios) limita la corriente del LED, determina el brillo de los LED.

Las señales de los canales izquierdo y derecho están conectadas a las entradas del convertidor analógico a digital ADC0 y ADC1. El tiempo de descenso del led de pico es de unos 600 ms.

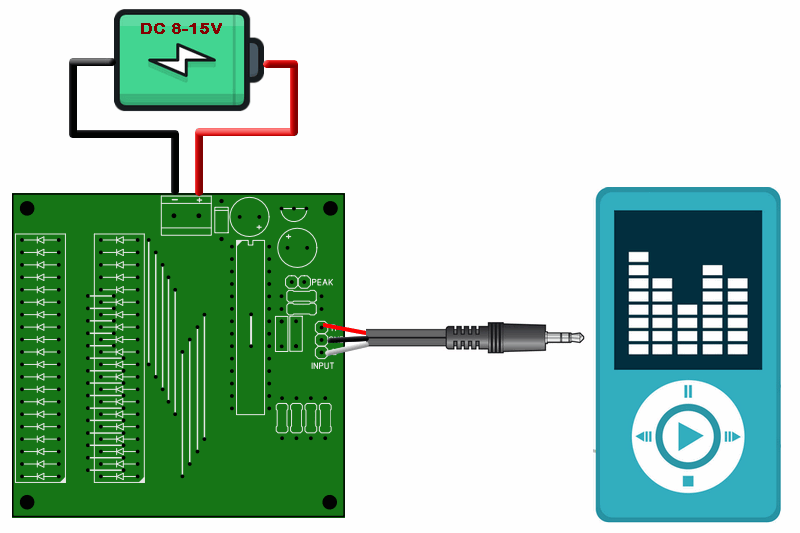

Puede hacer funcionar el circuito del medidor Vu con una fuente de alimentación de CC de 8 a 15 Voltios,. Si desea hacerlo funcionar con 5 V, no necesita usar un regulador 78L05.

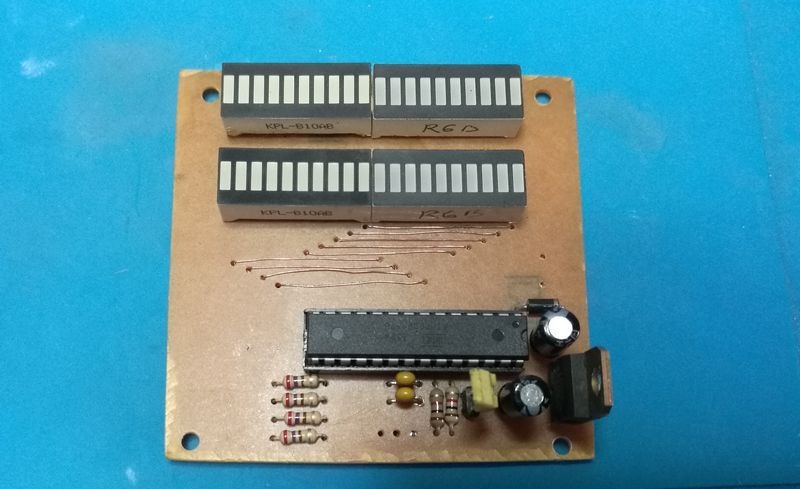

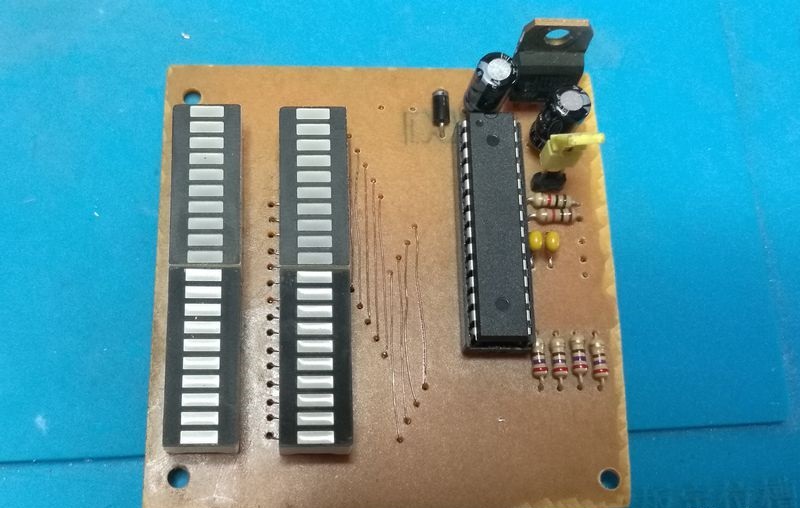

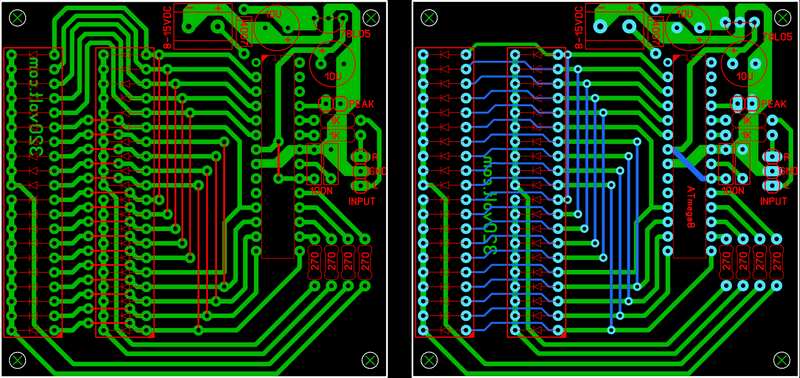

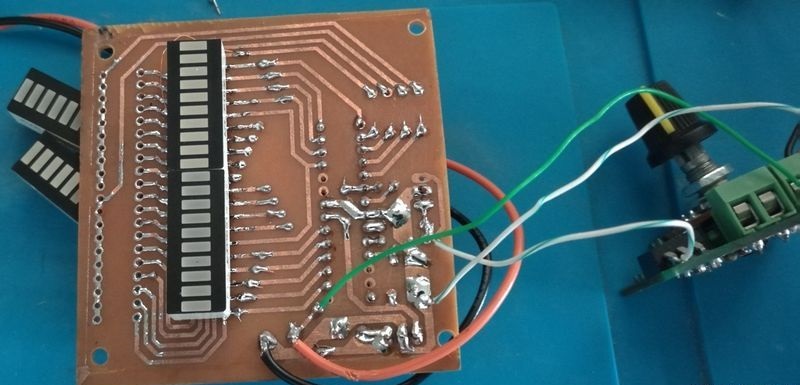

PCB El diseño del circuito impreso se preparó con el diseño Sprint. Las dimensiones de la PCB son 67x65 mm. Hay versiones de uno y dos niveles del diseño de PCB.

Se ha probado la PCB de una sola capa, no creo que haya un problema con la doble capa, no hay grandes cambios, los saltos se han movido a la capa superior. Si no encuentra barras de 20 LEDs, puede utilizar dos gráficos de barras de 10 LED en su lugar.

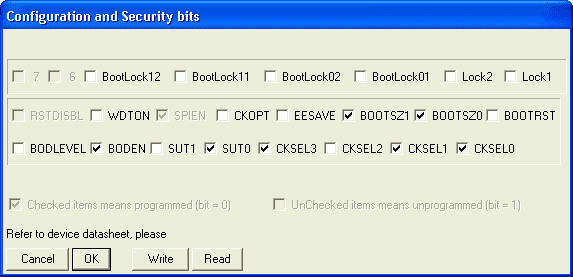

Cargue el software con ponyprog usando el circuito Programador Atmel simple (ISP de puerto serie). El circuito del medidor de VU tiene códigos fuente .asm y hexadecimal. Los ajustes de los fusibles ATmega8 en PonyProg se muestran a continuación. (Los valores hexadecimales son: fusible bajo: A4, fusible alto: D9).

Puede utilizar un reproductor de mp3, teléfono, computadora, etc. como fuente de audio. Se puede usar o se puede usar con un preamplificador de micrófono.

Código avr_iv2.asm

Código: Seleccionar todo

; Stereo indikator vybuzeni s ATmega8A / 8 / 8L

; int. RC 8MHz, BOD 2,7V

; IX. 2013

; vytvoril: DANYK

; http://danyk.cz/avr_iv2.html

.NOLIST

.INCLUDE "m8def.inc"

.LIST

.DEF REG=R16 ; docasny registr

.DEF REG2=R17 ; docasny registr 2

.DEF VYS_L=R18 ; vysledek AD prevodu dolni

.DEF VYS_H=R19 ; vysledek AD prevodu horni

.DEF DELREG=R20 ; registr deleni frekvence

.DEF DELREG2=R21 ; registr deleni frekvence 2

.DEF KANAL=R22 ; prepinani kanalu

.DEF MULTREG=R23 ; registr si pamatuje stav multiplexu

.DEF LK=R24 ; levy kanal

.DEF PK=R25 ; pravy kanal

.DEF LKD=R26 ; levy kanal indikace maxima

.DEF PKD=R27 ; pravy kanal indikace maxima

.DEF LKZ=R28 ; levy kanal zpozdeni maxima

.DEF PKZ=R29 ; pravy kanal zpozdeni maxima

.EQU SMER=DDRD

.EQU PORT=PORTD

.EQU SMER2=DDRC

.EQU PORT2=PORTC

.EQU VSTUPY=PINC

.EQU SMER3=DDRB

.EQU PORT3=PORTB

.CSEG

.ORG 0

RJMP START

; vektory preruseni

.ORG OC2addr ;preruseni citacem2 ridici multiplex, obnovovaci frekvenci

RJMP CASOVANI

START:

;nastaví port D

LDI REG,0b11111111

OUT SMER,REG

LDI REG,0b00000000

OUT PORT,REG

;nastaví port C

LDI REG,0b000000

OUT SMER2,REG

LDI REG,0b111100

OUT PORT2,REG

;nastaví port B

LDI REG,0b00111111

OUT SMER3,REG

LDI REG,0b11111100

OUT PORT3,REG

LDI REG,LOW(RAMEND)

OUT SPL,REG

LDI REG,HIGH(RAMEND)

OUT SPH,REG

LDI DELREG,1

LDI DELREG2,1

LDI MULTREG,1

CLR LK

CLR PK

CLR LKD

CLR PKD

CLR LKZ

CLR PKZ

; NASTAVENI CASOVACE A JEHO PRERUSENI

LDI REG,0b00001001 ; nulovani pri dosazeni porovnavane hodnoty...

OUT TCCR2,REG ; ...(tzv. CTC), OC0 nevyuzit. preddeli 1

LDI REG,249 ; nastavi porovnavanou hodnotu (dělí se n+1)

OUT OCR2,REG ;

LDI REG,0b10000000 ; povoli preruseni CTC OCIE2

OUT TIMSK,REG ;

;NASTAVENI ADC a MCU

; povoli uspani (sleep) a nastavi mod ADC nr

LDI REG,0b10010000

OUT MCUCR,REG

; vypne analog. komparator - neni nikdy vyuzit (setri energii)

LDI REG,0b10000000

OUT ACSR,REG

; nastavi ADC - f/8, povoli ho

LDI REG,0b10000011

OUT ADCSRA,REG

SEI ;povoli globalni preruseni

;hlavni smycka

SMYCKA:

SLEEP

RJMP SMYCKA

MULT:

LDI REG,0b00000000

OUT PORT,REG

LDI REG,0b11111100

OUT PORT3,REG

LDI REG,0b111100

OUT PORT2,REG

; rychle

CP LK,MULTREG

BRLO L_NE

CBI PORT3,2

L_NE:

MOV REG,MULTREG

SUBI REG,246

CP LK,REG

BRLO L2_NE

CBI PORT3,3

L2_NE:

CP PK,MULTREG

BRLO P_NE

CBI PORT3,4

P_NE:

MOV REG,MULTREG

SUBI REG,246

CP PK,REG

BRLO P2_NE

CBI PORT3,5

P2_NE:

; pomale

IN REG,VSTUPY

SBRC REG,2

RJMP MAX_VYP

CP LKD,MULTREG

BRNE LD_NE

CBI PORT3,2

LD_NE:

MOV REG,MULTREG

SUBI REG,246

CP LKD,REG

BRNE L2D_NE

CBI PORT3,3

L2D_NE:

CP PKD,MULTREG

BRNE PD_NE

CBI PORT3,4

PD_NE:

MOV REG,MULTREG

SUBI REG,246

CP PKD,REG

BRNE P2D_NE

CBI PORT3,5

P2D_NE:

MAX_VYP:

;vetveni multiplexu

MOV REG,MULTREG

DEC REG

LDI ZL,LOW(SKOK)

LDI ZH,HIGH(SKOK)

ADD ZL,REG

CLR REG

ADC ZH,REG

IJMP

SKOK:

RJMP MULT1

RJMP MULT2

RJMP MULT3

RJMP MULT4

RJMP MULT5

RJMP MULT6

RJMP MULT7

RJMP MULT8

RJMP MULT9

RJMP MULT10

MULT1:

SBI PORT,0

RET

MULT2:

SBI PORT,1

RET

MULT3:

SBI PORT,2

RET

MULT4:

SBI PORT,3

RET

MULT5:

SBI PORT,4

RET

MULT6:

SBI PORT,5

RET

MULT7:

SBI PORT,6

RET

MULT8:

SBI PORT,7

RET

MULT9:

SBI PORT3,0

RET

MULT10:

SBI PORT3,1

RET

PADEJ:

CPI LK,0

BREQ LEVY_0

DEC LK

LEVY_0:

CPI PK,0

BREQ PRAVY_0

DEC PK

PRAVY_0:

CPI LKZ,0

BREQ LEVYZ_0

DEC LKZ

RJMP LEVYZ_NE0

LEVYZ_0:

MOV LKD,LK

LEVYZ_NE0:

CPI PKZ,0

BREQ PRAVYZ_0

DEC PKZ

RJMP PRAVYZ_NE0

PRAVYZ_0:

MOV PKD,PK

PRAVYZ_NE0:

RET

; preruseni ridici multiplex a zdroj casovani

CASOVANI:

IN VYS_L,ADCL

IN VYS_H,ADCH

MOV REG,KANAL

ANDI REG,0b00000001

ORI REG,0b11000000 ;interni reference 2,56V, zarovna vpravo, vstup 0 / 1

OUT ADMUX,REG

SBI ADCSRA,6

CLR REG

LDI REG2,HIGH(11)

CPI VYS_L,LOW(11)

CPC VYS_H,REG2

BRLO MENSI2

INC REG

LDI REG2,HIGH(14)

CPI VYS_L,LOW(14)

CPC VYS_H,REG2

BRLO MENSI2

INC REG

LDI REG2,HIGH(18)

CPI VYS_L,LOW(18)

CPC VYS_H,REG2

BRLO MENSI2

INC REG

LDI REG2,HIGH(22)

CPI VYS_L,LOW(22)

CPC VYS_H,REG2

BRLO MENSI2

INC REG

LDI REG2,HIGH(28)

CPI VYS_L,LOW(28)

CPC VYS_H,REG2

BRLO MENSI2

INC REG

LDI REG2,HIGH(36)

CPI VYS_L,LOW(36)

CPC VYS_H,REG2

BRLO MENSI2

INC REG

LDI REG2,HIGH(45)

CPI VYS_L,LOW(45)

CPC VYS_H,REG2

BRLO MENSI2

INC REG

LDI REG2,HIGH(56)

CPI VYS_L,LOW(56)

CPC VYS_H,REG2

BRLO MENSI2

INC REG

LDI REG2,HIGH(71)

CPI VYS_L,LOW(71)

CPC VYS_H,REG2

BRLO MENSI2

INC REG

LDI REG2,HIGH(90)

CPI VYS_L,LOW(90)

CPC VYS_H,REG2

BRLO MENSI2

INC REG

RJMP POPOSKOC

MENSI2:

RJMP MENSI

POPOSKOC:

LDI REG2,HIGH(113)

CPI VYS_L,LOW(113)

CPC VYS_H,REG2

BRLO MENSI

INC REG

LDI REG2,HIGH(142)

CPI VYS_L,LOW(142)

CPC VYS_H,REG2

BRLO MENSI

INC REG

LDI REG2,HIGH(179)

CPI VYS_L,LOW(179)

CPC VYS_H,REG2

BRLO MENSI

INC REG

LDI REG2,HIGH(225)

CPI VYS_L,LOW(225)

CPC VYS_H,REG2

BRLO MENSI

INC REG

LDI REG2,HIGH(283)

CPI VYS_L,LOW(283)

CPC VYS_H,REG2

BRLO MENSI

INC REG

LDI REG2,HIGH(356)

CPI VYS_L,LOW(356)

CPC VYS_H,REG2

BRLO MENSI

INC REG

LDI REG2,HIGH(449)

CPI VYS_L,LOW(449)

CPC VYS_H,REG2

BRLO MENSI

INC REG

LDI REG2,HIGH(565)

CPI VYS_L,LOW(565)

CPC VYS_H,REG2

BRLO MENSI

INC REG

LDI REG2,HIGH(711)

CPI VYS_L,LOW(711)

CPC VYS_H,REG2

BRLO MENSI

INC REG

LDI REG2,HIGH(895)

CPI VYS_L,LOW(895)

CPC VYS_H,REG2

BRLO MENSI

INC REG

MENSI:

INC KANAL

SBRC KANAL,0

RJMP LEVY_NE

CP LK,REG

BRSH L_NENI_VYSSI

MOV LK,REG

L_NENI_VYSSI:

CP REG,LKD

BRLO LD_JE_NIZSI

LDI LKZ,67 ;zpozdeni

MOV LKD,REG

LD_JE_NIZSI:

RJMP PRAVY_NE

LEVY_NE:

CP PK,REG

BRSH P_NENI_VYSSI

MOV PK,REG

P_NENI_VYSSI:

CP REG,PKD

BRLO PD_JE_NIZSI

LDI PKZ,67 ;zpoždění

MOV PKD,REG

PD_JE_NIZSI:

PRAVY_NE:

DEC DELREG

BRNE HOP

LDI DELREG,32

RCALL MULT

DEC MULTREG

BRNE HOP

LDI MULTREG,10

DEC DELREG2

BRNE HOP

LDI DELREG2,3 ; !!! DOBA SESTUPU / FALL TIME (2 = 400ms, 3 = 600ms, 4 = 800ms, 5 = 1s, ...) !!!

RCALL PADEJ

HOP:

RETI

Código: Seleccionar todo

:020000020000FC

:0200000003C03B

:1000060088C00FEF01BB00E002BB00E004BB0CE3BD

:1000160005BB0FE307BB0CEF08BB0FE50DBF04E004

:100026000EBF41E051E071E088279927AA27BB2738

:10003600CC27DD2709E005BD09EF03BD00E809BFB0

:1000460000E905BF00E808B903E806B97894889581

:10005600FECF00E002BB0CEF08BB0CE305BB871725

:1000660008F0C298072F065F801708F0C398971705

:1000760008F0C498072F065F901708F0C59803B3D9

:1000860002FD10C0A71709F4C298072F065FA01734

:1000960009F4C398B71709F4C498072F065FB01779

:1000A60009F4C598072F0A95EDE5F0E0E00F002763

:1000B600F01F099409C00AC00BC00CC00DC00EC0C9

:1000C6000FC010C011C012C0909A0895919A089559

:1000D600929A0895939A0895949A0895959A0895F0

:1000E600969A0895979A0895C09A0895C19A089580

:1000F600803009F08A95903009F09A95C03011F059

:10010600CA9501C0A82FD03011F0DA9501C0B92FD9

:10011600089524B135B1062F0170006C07B9369ADF

:10012600002710E02B30310778F1039510E02E30D0

:10013600310750F1039510E02231310728F103957C

:1001460010E02631310700F1039510E02C3131071C

:10015600D8F0039510E024323107B0F0039510E093

:100166002D32310788F0039510E02833310760F00F

:10017600039510E02734310738F0039510E02A354F

:10018600310710F0039501C032C010E02137310766

:1001960070F1039510E02E38310748F1039510E011

:1001A600233B310720F1039510E0213E3107F8F09B

:1001B600039511E02B313107D0F0039511E0243679

:1001C6003107A8F0039511E0213C310780F0039533

:1001D60012E02533310758F0039512E0273C31072A

:1001E60030F0039513E02F37310708F00395639538

:1001F60060FD08C0801708F4802F0A1710F0C3E4CA

:10020600A02F07C0901708F4902F0B1710F0D3E417

:10021600B02F4A9549F440E21CDF7A9529F47AE03A

:0A0226005A9511F453E064DF1895B7

:00000001FF